Na dzisiejszym konkurencyjnym i gwałtownie zmieniającym się rynku elektroniki, szybkość i efektywność testowania produktów ma znaczący wpływ na szybkość wprowadzenia produktu na rynek i jego jakość. Zwiększający się stopień skomplikowania układów scalonych, rosnąca ilość wyprowadzeń i wielowarstwowe obwody drukowane tworzą wiele problemów przy strukturalnym I funkcjonalnym testowaniu elektroniki. Niektóre można wskazać jak następuje:

- Brak dostępu do wyprowadzeń układów scalonych i wewnętrznych warstw obwodów drukowanych dla przeprowadzenia pomiaru parametrów elektrycznych.

- Złożona struktura i długi czas przygotowania testów

- Trudna automatyzacja procesu testowania i analizy wyników testów

- Ograniczenia pokrycia testami i szczegółowej diagnostyki

i ostatnie lecz równie ważne

- Integracja procesu programowania mikrokontrolerów, pamięci flash, PLD, w układzie docelowym w ramach procesu testowania

Dotychczas stosowane metody testowania funkcjonalnego i ostrzowego strukturalnego ICT (In-Circuit Testing) tracą swoją skuteczność w raz z wchodzącymi nowymi technologiami – zwiększaniem skali integracji i stopnia komplikacji projektów. Istnieje więc potrzeba zmiany podejścia do testowania i kontroli jakości. Od początku procesu projektowania nowego urządzania trzeba mieć na względzie to jak będziemy nasze urządzenie testować. Trzeba projektować pod kątem jego testowalności (Design-For Testability - DFT). Boundary-Scan (B-S) zwana skanowaniem ścieżki krawędziowej jest jedną z najbardziej efektywnych dostępnych metod testowania i programowania w układzie docelowym. Bazuje ona na specjalnym układzie elektronicznym wbudowanym w strukturę układu scalonego i umożliwiającym ustawianie i odczyt stanu sygnałów na wewnętrznych wyprowadzeniach układu.

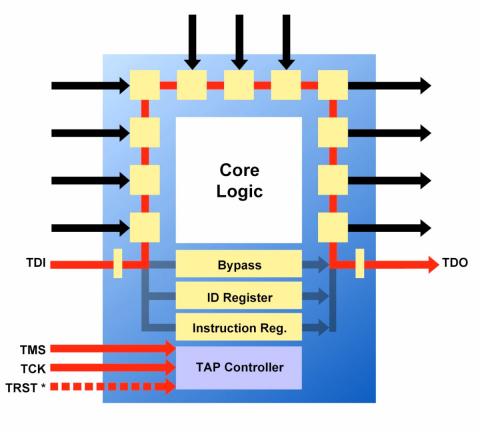

Struktura układu scalonego z zaimplementowanym B-S

Technologia testowania Boundary-Scan została wprowadzona przez niezależny zespół ekspertów m.in. z firm Philips,BT, GEC,TI znany jako grupa JTAG (Joint Test Action Group), która odbyła szereg roboczych spotkań w końcówce lat 80-tych. W 1990 technologia ta stała się standardem IEEE1149.1. Od tamtego czasu stale zyskiwała na popularności ponieważ coraz więcej producentów półprzewodników wprowadzała coraz więcej układów kompatybilnych z tym standardem. Dzisiaj dostępna jest ogromna ilość układów z wbudowanym B-S, a tysiące linii produkcyjnych wykorzystuje tę technologię do automatycznego testowania płytek elektronicznych i programowania układów na nich zamontowanych.

Aby spełnić standard układ musi zawierać:

- 4-liniowy (5-liniowy jeśli stosowany jest opcjonalny sygnał reset) port/interfejs dostępu TAP (Test Access Port)

- Wewnętrzne komórki B-S buforujące wszystkie wyprowadzenia układu

- Wewnętrzne zdefiniowane przez standard rejestry B-S

- Układ multiplexiowania sygnałów

Dodatkowo producenci układów muszą dostarczyć pliki BSDL (Boundary-Scan Desription Language), które opisują implementację B-S w danym układzie. Stanowi to klucz do automatyzacji generowania testów, ich realizacji i analizy wyników. Więc …

Aby umożliwić testowanie metodą B-S po pierwsze w projekcie trzeba użyć układów kompatybilnych z IEEE1149.1 – im więcej tym większe pokrycie testami. To wymaganie jest stosunkowo łatwo spełnić. Większość złożonych układów scalonych jak mikrokontrolery, PLD, … mają wbudowane mechanizmy B-S. Co więcej, aby osiągnąć dobre pokrycie testami, nie jest konieczne stosowanie wszystkich układów spełniających normę IEEE1149.1. Mogą w układzie być bloki (tzw. cluster) otoczone układami B-S, a złożone z układów bez wbudowanego mechanizmu B-S. Wówczas takie obszary są testowalne na zasadzie wymuszania i odczytu stanu sygnałów na liniach komunikacyjnych tego bloku przez infrastrukturę B-S otaczających je układów. Ma to miejsce na przykład gdy na płytce drukowanej są pamięci sterowane z mikrokontrolera, PLD, …

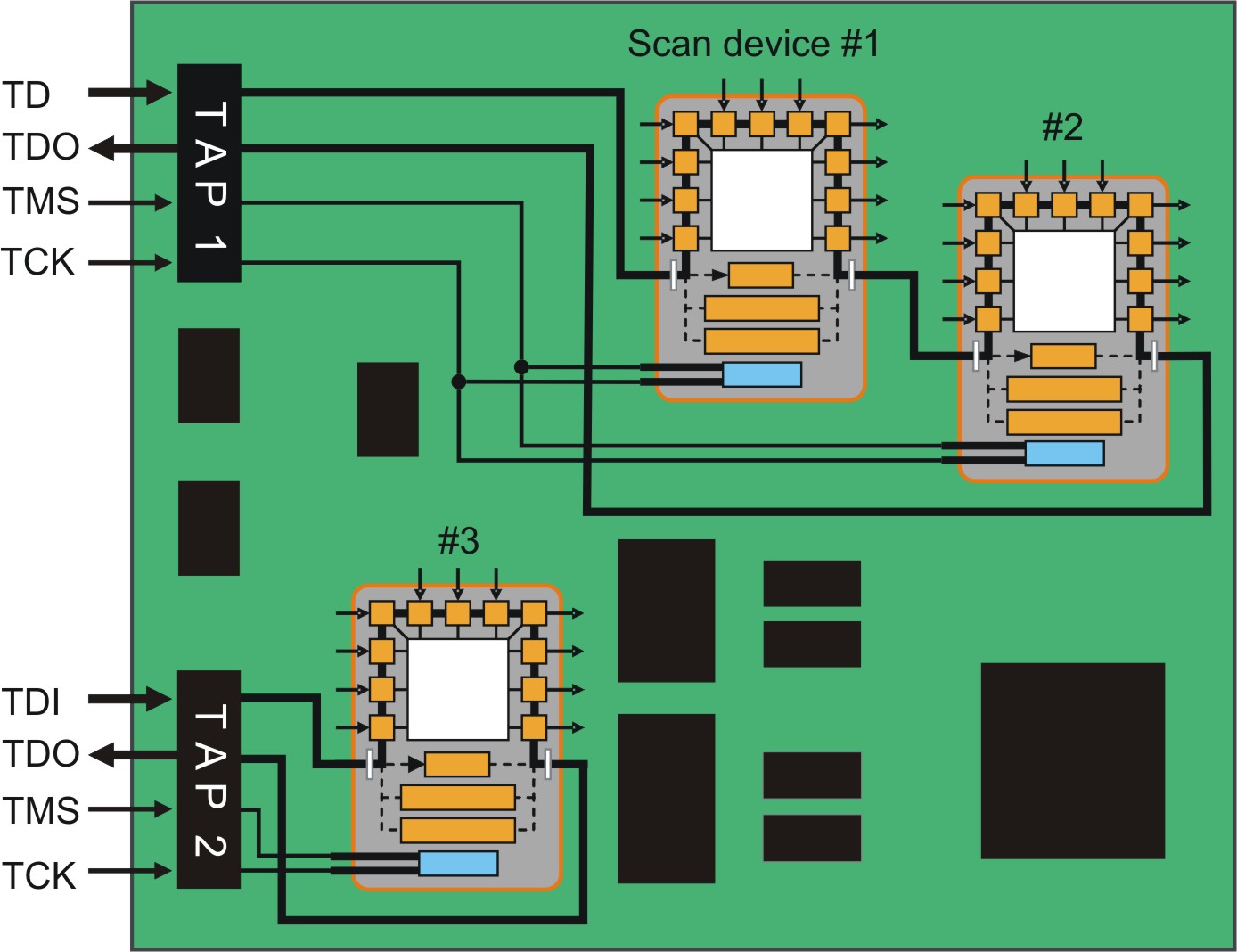

Infrastruktura łańcucha połączeń B-S na płytce

Następnie trzeba zaprojektować płytkę drukowaną tak aby zapewnić dostęp do infrastruktury B-S zamontowanych na niej układów. W tym celu należy połączyć sygnały portów TAP poszczególnych układów B-S szeregowo w łańcuch – linię TDO (Data Output) jednego układu z linią TDI (Data Input) drugiego itd. Sterowanie infrastrukturą testową B-S na płytce zawierającą m.in. rejestry przesuwne, realizowane jest równolegle sygnałami TCK (Test Clock) i TMS (Test Mode Select). Sygnał zerowania TRST (Reset) jest opcjonalny. Dla zrównoleglenia i przyspieszenia procesu testowania poszczególnych bloków funkcjonalnych można na płytce zrealizować kilka łańcuchów.

I tak sekwencyjny łańcuch połączeń sygnałów B-S poszczególnych układów realizuje dostęp za pośrednictwem portów TAP do wszystkich wyprowadzeń wszystkich układów B-S umożliwiając ustawianie i odczyt stanu poszczególnych komórek B-S związanych z fizycznymi wyprowadzeniami układów. Testowanie odbywa się więc na zasadzie wymuszenia stanu na umownych wejściach i odczytu odpowiedzi na umownych wyjściach.

W normalnych operacjach układy B-S funkcjonują tak jakby nie zawierały infrastruktury B-S, jakby była ona przezroczysta. Natomiast w trakcie testowania lub programowania ISP logika B-S jest aktywowana. Wówczas dane mogą być szeregowo przesłane do układów połączonych w łańcuch B-S i odczytane z nich. Te dane mogą być wykorzystane to stymulacji samego układu scalonego, do wysterowania sygnałów na zewnątrz w ramach pakietu PCB, detekcji sygnałów i odpowiedzi na te wymuszenia. Różne dostępne tryby skanowania umożliwiają testowanie pojedynczych płyt PCB lub nawet całych systemów wielomodułowych w zakresie strukturalnych błędów montażu oraz programowanie mikrokontrolerów, pamięci, PLD już zamontowanych. To wszystko za pośrednictwem standardowego portu/interfejsu TAP.

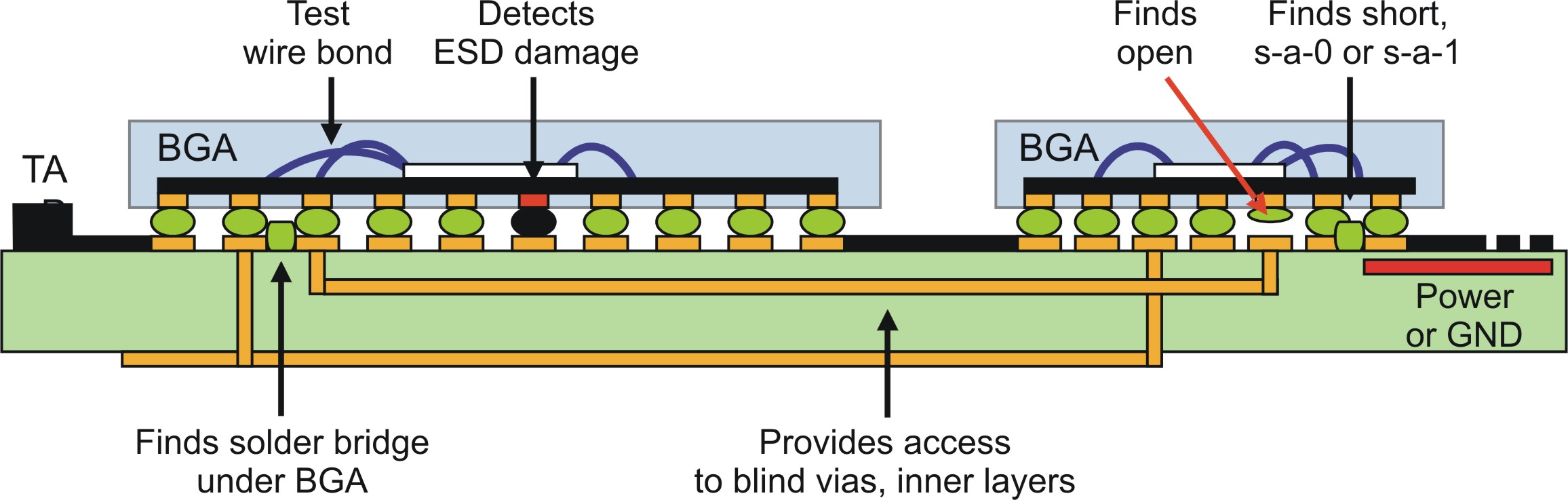

Biorąc pod uwagę, że komórki B-S związane z wyprowadzeniami układów są w środku struktury półprzewodnika, testowanie metodą B-S jest “głębsze” niż przy stosowaniu testerów ostrzowych – testowane są połączenia między wewnętrznymi komórkami układów zamiast między zewnętrznymi ich wyprowadzeniami..

Uszkodzenia możliwe do wykrycia metodą B-S

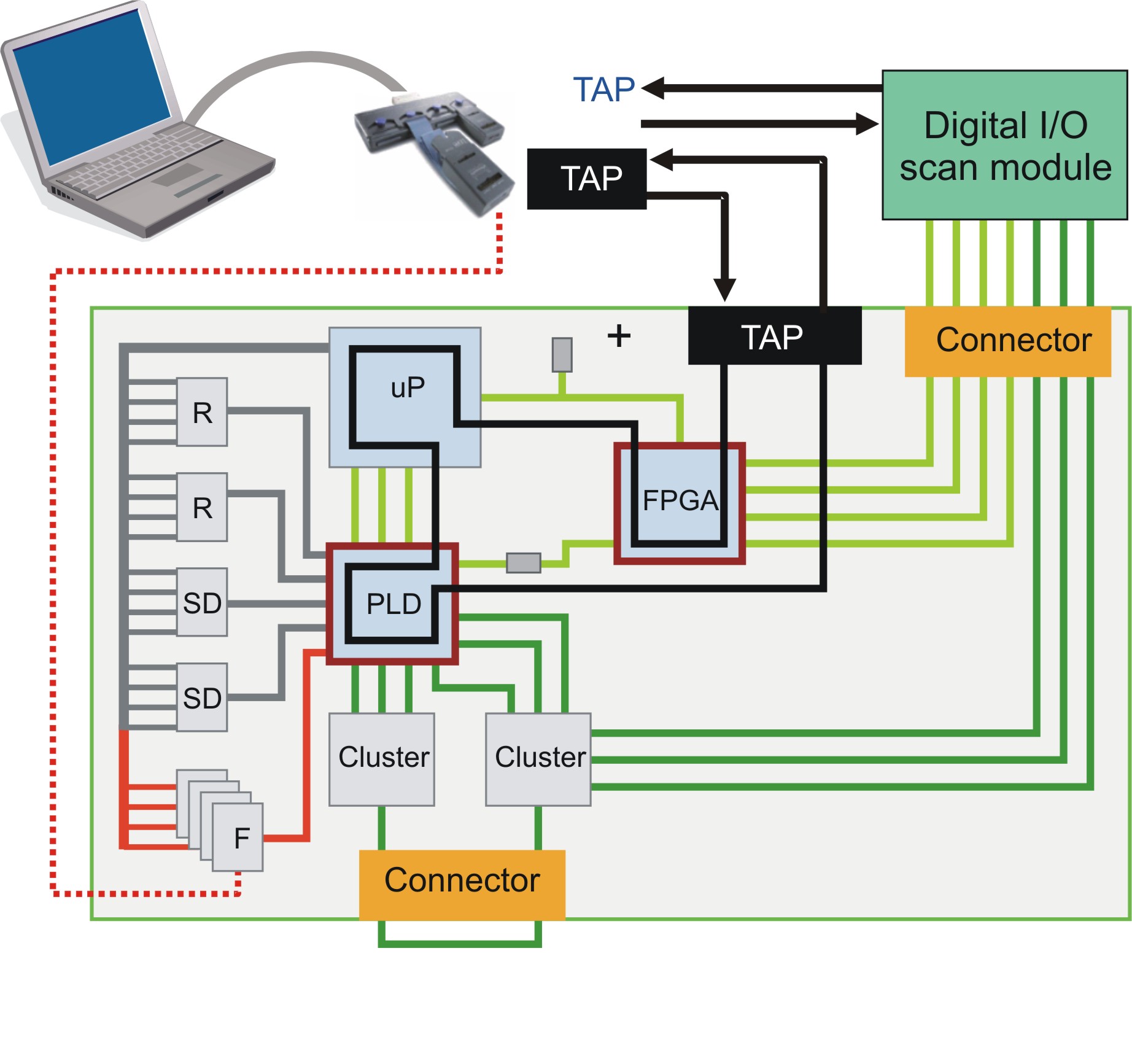

Aby przeprowadzić testy i analizować ich wyniki testowany pakiet musi być podłączony do komputera PC za pośrednictwem dedykowanego kontrolera i portu interfejsu TAP. Dodatkowo specjalne moduły we/wy cyfrowych rozszerzają technologie B-S o możliwość testowania złącz i linii interfejsowych pakietu. Następnym krokiem może być testowanie całych systemów zbudowanych z wielu płyt.

Struktura system testowania bazującego na B-S

Dostępne oprogramowanie pozwala automatycznie lub półautomatycznie generować testy, wykonywać je, wizualizować i analizować wyniki. JTAG Technologies oferuje pełny zakres produktów sprzętowych i programowych do obsługi infrastruktury B-S. Z racji wieloletniego doświadczenia zapewnia wsparcie na najwyższym poziomie technicznym i handlowym.

Process testowania B-S może być integrowany z testerami automatycznymi ATE (Automatic Test Equipment). JTAG Technologies współpracuje w tym zakresie z producentami testerów ICT (In-Circuit Testers), FPT (Flying Probes Testers) i FT(Functional Testers).

Założyciele JTAG Technology byli zaangażowani w tworzenie technologii B-S i standardu IEEE1149.1 od samego początku. Norma definiuje logikę do wbudowania w układ scalony, która może być wykorzystana na poziomie zmontowanej płytki drukowanej do przeprowadzenia precyzyjnych testów strukturalnych i zapisywania zamontowanych już układów programowalnych. Od czasu zdefiniowania standardu w 1990 roku był on już dwukrotnie uaktualniany i cztery nowe normy rozszerzające zostały zdefiniowane:

- IEEE 1149.4 – definiuje analogowe B-S

- IEEE 1149.6 - rozszerza możliwości B-S poza pierwotny cyfrowy obszar zastosowań

- IEEE 1532 - ustanawia wspólny opisowy format dla urządzeń programowalnych jak PLD i FPGA

- IEEE 1149.7 - redukuje ilość sygnałów i rozszerza funkcjonalność połączeń między systemem testującym a układem docelowym.

Trwają prace nad dalszymi rozszerzeniami technologii B-S. Są wśród nich:

- IEEE P1149.1-2013 - pełna norma i aktualizacja 1149.1,

- IEEE P1149.8 – rozszerzenie dla współpracy z czujnikami pojemnościowymi,

- IEEE 1581 - rozszerzenie dla układów pamięci,

- IEEE P1687 - rozszerzenie dla współpracy z wbudowanymi w układ przyrządami testującymi,

- SJTAG - rozszerzenie dla testowania na poziomie systemu.

JTAG Technologies wdraża wszystkie te nowości by zachować wiodącą pozycję na rynku i najwyższy poziom techniczny swoich produktów.